CoolSem wants to make III-V chips run cooler, harder, longer

Eindhoven startup unveils wafer-level thermal pathway for lasers, RF and power devices, tackling one of deep tech’s limiting problems: heat.

Published on September 20, 2025

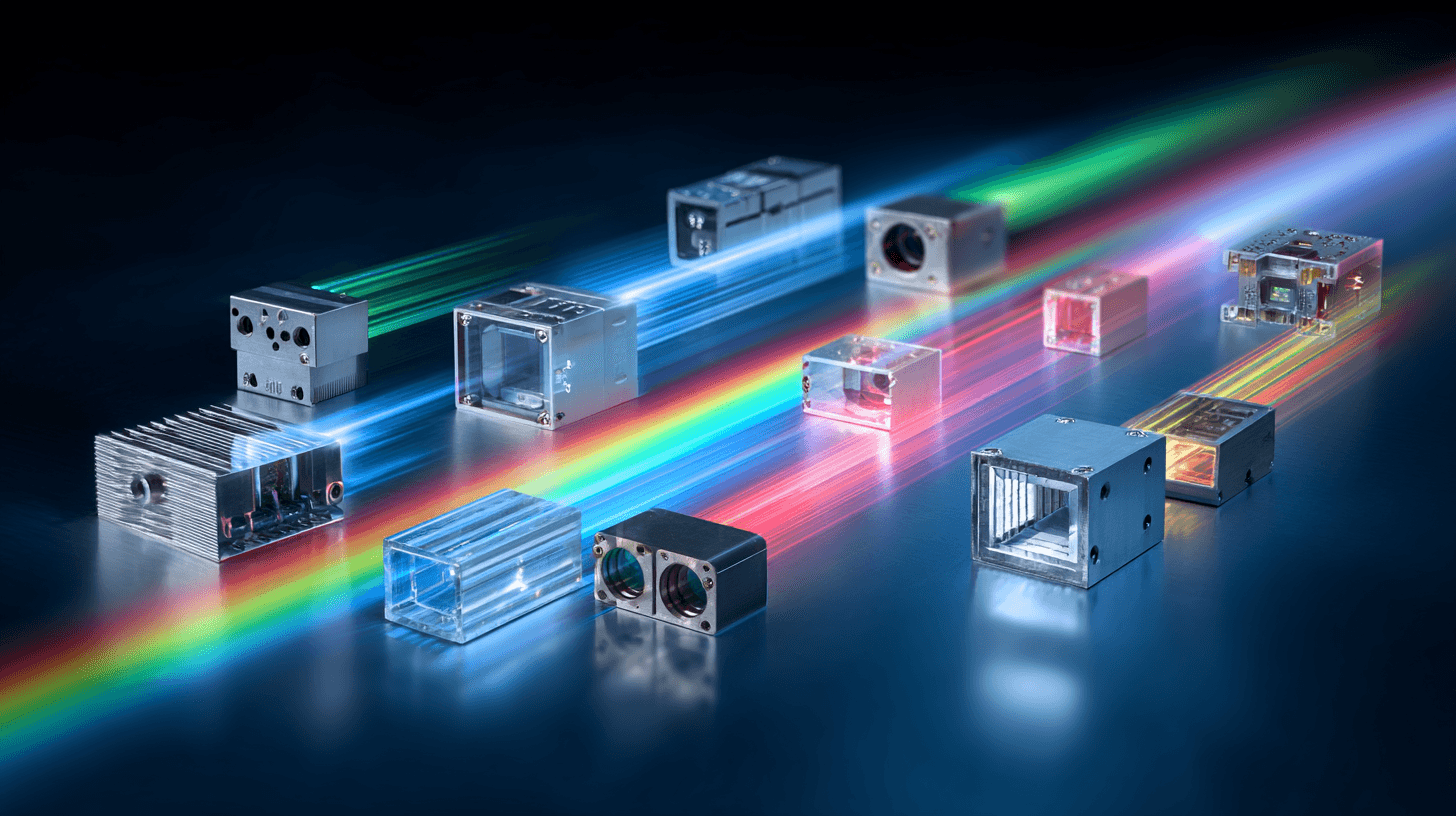

CoolSem’s technology focuses on applications in telecom, sensing, space, and consumer electronics - requiring exceptional performance, efficiency, or reliability.

Bart, co-founder of Media52 and Professor of Journalism oversees IO+, events, and Laio. A journalist at heart, he keeps writing as many stories as possible.

When chips hit their performance ceiling, it’s usually not physics in the abstract; it’s temperature. Self-heating throttles output power, shifts operating points, and shortens lifetimes. The problem is especially acute in III-V semiconductors (such as GaAs, InP, and GaN): they enable blistering speeds and photons-on-demand, but their substrates are mediocre heat conductors.

Indium phosphide’s and gallium arsenide’s thermal conductivity is orders of magnitude lower than copper, so heat struggles to escape, degrading performance in photonics, RF, and high-power electronics. Eindhoven-based CoolSem Technologies, newly out of stealth at High Tech Campus, proposes a deceptively simple fix: remove the thermal bottleneck itself. The startup’s thin-film flow removes the III-V substrate and bonds the now ultra-thin device directly onto a heat-spreading layer or heatsink, creating a short, efficient path from the junction to the copper. The substrate can be reused, and the process is pitched as cost-effective and compatible with established supply chains.

CoolSem calls its platform WaLTIS, which stands for Wafer-Level Thermal Interface Stack. In a recent SEMI write-up, the company claims that WaLTIS can deliver up to 15 times better thermal management and 25–55 °C lower chip temperatures, boosting performance and reliability while reducing cooling energy by 30–50%. If those gains hold across device classes, they open new headroom for designers who have been forced to de-rate to stay within safe junction temperatures.

Why this matters now

The heat problem is getting worse, not better. In photonics, high-brightness lasers and dense integrated optics pack more watts into smaller footprints. In RF power, GaN HEMTs continue to push power density; in power electronics, wide-bandgap devices switch faster and hotter. III-V substrates simply don’t evacuate heat well, so the interface from device to heatsink is decisive.

Industry has tried several workarounds:

- Diamond heat spreaders / GaN-on-diamond. Integrating chemical-vapor-deposited (CVD) diamond near the hotspot has reduced device peak temperatures by ~25–40% in laboratory and pilot deployments, and increased RF power density compared to GaN-on-SiC. It works, but material and processing costs remain high and integration is non-trivial.

- Phase-change and gap-filler TIMs. These are inexpensive and assembly-friendly, but their limited thermal conductivity makes them unsuitable as the primary path for extreme heat fluxes.

- Microfluidic and two-sided liquid cooling. Brilliant for data-center silicon and some 3D-IC stacks, but complex for discrete III-V devices and not a drop-in to typical RF/power packages.

CoolSem’s bet is that wafer-level substrate removal combined with a stack engineered for thermal conductivity, mechanical support, RF isolation, and CTE management can unlock much of diamond’s benefits at a lower cost and with better manufacturability. The company also emphasizes the reuse of expensive GaAs/InP wafers, a non-trivial sustainability and cost lever for photonics lines.

What’s inside WaLTIS (and what it must beat)

Without disclosing full-stack chemistry on its website, CoolSem positions WaLTIS as a wafer-level thermal interface that allows direct attach to standard copper heatsinks. That matters because copper’s conductivity dwarfs CuMo/CuW, the usual 'safe' bases used to match the chip’s thermal expansion - hence the promise of both higher output power and lower cost. In adjacent literature, direct-attach flows typically lean on established joining methods like AuSn solder (common in laser die attach) and Ag sintering (now mainstream in high-reliability power modules). Therefore, if WaLTIS plays nicely with those, adoption risk drops.

There’s also an evidence base for CoolSem’s thin-film premise: research teams have shown that thin-film VCSELs or III-V devices bonded to high-conductivity metal stacks/copper plates reduce thermal resistance and raise peak power compared to bulk devices on their native substrates. That’s the same direction of travel CoolSem is industrializing.

The team behind the claim

CoolSem’s founding bench blends process, operations and commercial scar tissue from Eindhoven’s deep-tech scene:

- André van Geelen (CEO/CTO) has founded and scaled multiple high-tech businesses and held senior roles across semiconductors and RF systems; he also advises startups through Silicon Catalyst. That mix of III-V domain depth and company-building will be pivotal as CoolSem moves from POC to production.

- Robbert van der Waal (CSO) previously led business development and sales at the Philips MEMS Foundry on HTCE (now XIVER), where wafer-level thin-film and MEMS processes are the daily bread. He later joined XIVER’s management journey before turning to CoolSem. Expect him to translate WaLTIS into qual plans and customer roadmaps that device makers recognize.

- Kees Steenbergen (COO) ran operations at Pharrowtech, an Eindhoven fabless RF player, bringing a practical view on yield, packaging, and supply chains that can make or break a thermal technology in volume.

- Pieter Heersink (CCO) is a seasoned connector across photonics and semiconductors, with experience in business development (including roles with SmartNanotubes and regional innovation) and a strong network among early industrial adopters.

What to watch

- Independent validation. SEMI highlights are promising; the big tell will be third-party measurements on benchmark devices such as InP lasers, GaAs power amps, or GaN dies, versus CuW/CuMo baselines and diamond spreaders.

- Packaging compatibility. If WaLTIS is robust under AuSn/Ag-sinter attach and standard hermetic or overmold flows, it significantly reduces NPI friction.

- System-level economics. Cutting junction temperatures isn’t just about increasing watts; it can shrink heatsinks and fans, reduce cooling energy, and extend lifetime, which is crucial when data-center and telecom operators face rising energy bills. Diamond proves the physics; CoolSem must prove the cost/performance crossover.

High Tech Campus as a breeding ground

Eindhoven is an apt launchpad: the High Tech Campus concentrates expertise in thin-film, packaging, photonics, and MEMS, all essential ingredients for a wafer-level thermal stack to find its early believers. If CoolSem’s approach scales, it won’t just make hot chips cooler; it could tip the balance in product lines where the thermal budget quietly dictates what’s possible.

Watt Matters in AI

Watt Matters in AI is a conference that aims to explore the potential of AI with significantly improved energy efficiency. In the run-up to the conference, IO+ publishes a series of articles that describe the current situation and potential solutions. Click on the link to read them all.

Sources for this story: CoolSem website (problem/solution, team, location); thermal property references for GaAs/InP; conductivity of copper and CuMo/CuW; literature on thin-film devices and copper attach; diamond/ GaN-on-diamond benchmarks; phase-change TIM properties; microfluidic cooling context; founder bios via Silicon Catalyst, HTCE/XIVER, and LinkedIn posts.